首页>>公司介绍>>测试文集

手机:13401017970

邮箱:lxtest@lxtest.com.cn

电话:+86-10-8200-3193

+86-10-8200-3199

+86-10-8200-3186

传真:+86-10-8200-5988

邮编:100088

地址:北京市海淀区北三环中路31号

泰思特大厦1号楼

MOSFET和IGBT栅电荷测试方法介绍

李力军

(北京励芯泰思特测试技术有限公司,北京,100088)

摘要:

功率MOSFET与IGBT已经成为功率半导体应用中的主要器件,而MOSFET和IGBT栅电荷测试方法困扰用户已久。国内鲜有单位从事相关方面研究,为了更好地保障产品质量,本文就MOSFET和IGBT栅电荷测试方法进行了介绍。

关键词:MOSFET;IGBT;栅电荷

由于功率MOSFET与IGBT具有导通电阻(电压)低、击穿电压高、驱动简单的特点,目前已经成为功率半导体分立器件应用中的主要器件,广泛应用于计算机外设、电源(AC/DC、DC/DC、DC/AC变换器)、手机、汽车电子、音响电路及仪器仪表等领域。在上述应用中大部分MOSFET或IGBT是处于开关状态。正确使用这些器件,避免器件失效的发生,就需要理解并掌握MOSFET或IGBT的特性。功率MOSFET有两个重要的参数,一个是导通电阻RDS(on),另一个就是栅电荷Qg。国际上通用 FOM = Qg * Ron 作为优值函数来表征MOSFET器件的性能,

因此栅电荷和导通电阻具有非常重要的作用[1]。导通电阻是一个静态直流参数,比较容易测量,而栅电荷的测量对激励源和测试电路的要求较高,其中特别是被测器件负载对观察器件栅极电荷的特性并正确测量至关重要。本文将介绍MOSFET栅电荷的相关参数,结合美军标MIL-STD-750E 3471.2 介绍栅电荷的测试方法,以及测试中应注意的问题。IGBT的栅极电荷特性及测试方法与MOSFET相同,只需将MOSFET中的漏极D、源极S替换为集电极C和发射极E即可。

图1所示为一个常见的MOSFET器件外特性模型,此外还包括了驱动电路、总的栅极电阻以及漏极的一个负载阻抗。由器件手册给出的输入电容(Ciss)、输出电容(Coss)和反向电容(Crss),图1中的三个电容分别定义如下:

Ciss = Cgs + Cgd ; Coss = Cds + Cgd ; Crss = Cgd

其中栅漏电容Cgd 也称为米勒电容,是栅漏电压的非线性函数。静态下的栅漏电容比栅源电容小得多,但随着漏源电压VDS的变化,栅漏电容可增大至栅源电容的20倍[2]。因此栅漏电容Cgd对栅电荷的影响最大。

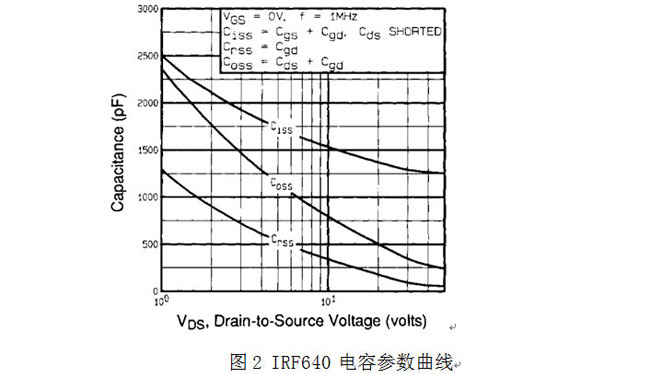

图2所示是取自IRF640的电容参数特性曲线,图中可以看出这些电容参数与VDS有关。Cgd是三个电容参数中的共同变量,因此可以理解为Ciss,Coss,Crss参数随VDS的改变是由于Cgd与Cds随VDS变化造成的,器件手册中给出的栅电荷参数是在特定条件下的测试结果,而一般寄生电容Cgs是恒定的。

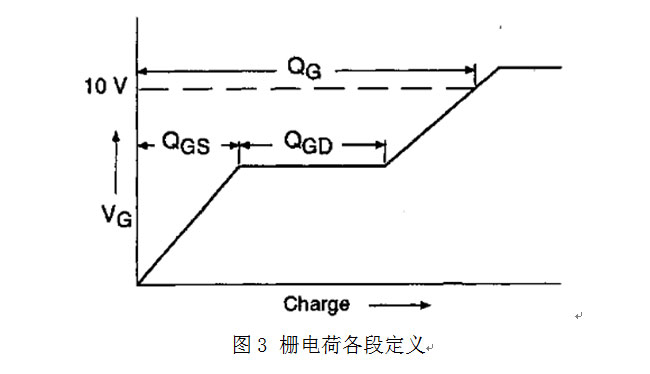

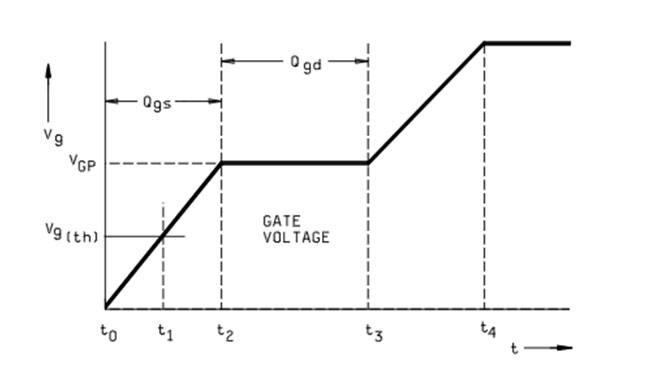

栅电荷一般由三个参数构成:Qg是栅极总电荷;Qgs是栅源电荷;Qgd是栅漏电荷,也即米勒效应电荷。图3所示为IRF640数据手册上的栅电荷曲线定义。从曲线中可以看到,Qgs起始与0点到第一个拐点的电荷,Qgd是电荷从第一个拐点到第二个拐点的电荷,Qg是从0点到VGS等于驱动峰值电压处的电荷。曲线中从第一个拐点到第二拐点处的曲线是一条平行直线,称为平台曲线。

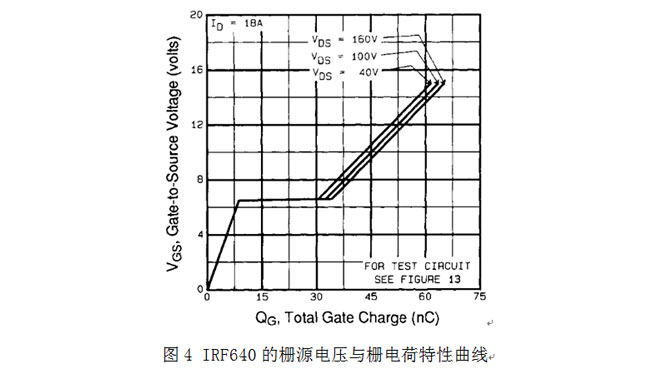

图4是IRF640数据手册栅极电压在恒流驱动时的特性曲线,曲线显示了当恒定电流流入器件栅极后,栅极电压VGS的大小与注入到栅极的电荷的关系。图中可以看出VDS对于栅电荷特性曲线中的平台阶段具有的影响。

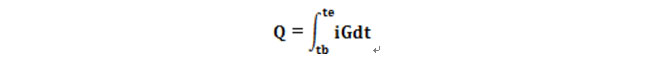

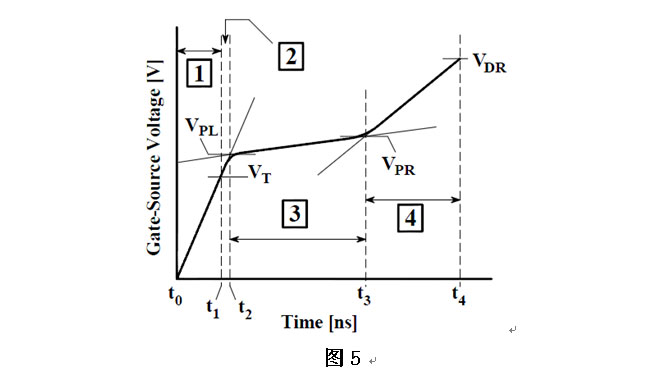

图4是栅源电压与栅电荷曲线,与之对应的栅源电压与充电时间曲线如图5所示。在测试栅电荷时,会在栅极施加一个恒流源以确定有多少电荷注入到器件栅极,由于电流定义为每秒钟通过导体截面的电荷量,因此栅电荷可以通过对时间积分求的:

当栅极电流恒定时,上式可简化:

因此,当图1中的栅极驱动为一个恒流源时,就可以将栅源电压与时间的特性曲线同栅源电压与电荷的曲线相对应起来。得到下述公式:

Qg = Ig * t

图5曲线中1~4的序号表示栅源电压VGS上升过程中存在四个阶段。虽然器件手册中给出的是三个阶段,但按图5分为四个充电阶段更便于分析:

第一阶段:

在第一阶段,栅源电压VGS从0点上升至开启电压VT,漏极电流ID没有流动,漏源电压VDS不变。此时器件处于关断状态,在t0时刻,对器件栅极施加恒流源,VGS开始上升并且对寄生电容Cgd和Cgs充电。第一阶段容易认为仅对Cgs充电,而当VGS上升时,Cgs应当也处于充电状态。当VDS不变时Cgs与Cgd相比大许多,因此会有更多电流对Cgs充电。此外需要注意的是,Cgs是与电压无关的寄生参数,但是Cgd和Cds均与它们两端电压差有关(当漏极电压高于栅极电压时Cgd与Cds与电容两端压差成反向关系),当栅极与漏极电压升高时,Cgd将减少,当漏极与源极电压升高时Cds也将减少。当VDS>VGS是,如果VGS升高,则会造成VGD减少,因此会引起Cgd升高。也就是说,当VGS升高时Cgd升高。因此,随着VGS升高,栅电荷会有轻微增加。

第二阶段:

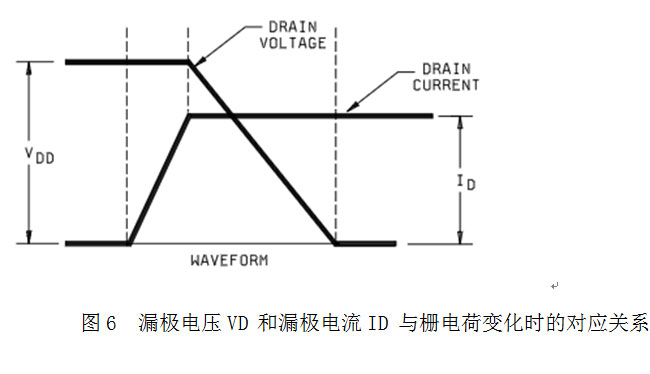

在第二阶段,栅源电压VGS从开启电压VT上升至平台电压VPL,漏源电压VDS开始减少,漏极电流开始流动。当漏极电流开始流动时(忽略漏流),所对应的栅源电压VGS称为开启电压。图6所示,t=t1时刻,ID开始流动并且VDS开始降低,到t=t2时刻时,曲线出现第一个拐点。在第一阶段,总的电荷累积量是由于恒流驱动源对寄生电容Cgs和Cgd充电的总效应,并且Cgd由于VGD的减少有轻微增加。在第二阶段,电荷的变化量将会随着Cgd和VGD的乘积变化,这是由于,其中V是电容两端电压差,C是容值。图1所示VGD的变化由漏极电流ID和漏极阻抗ZL决定。

如果如图1中使用电阻负载或者电感负载时,在第二阶段的拐点处,并不能保证ID电流达到最大,漏极电流ID应在拐点右侧达到最大。而当测试使用恒流源负载时,在理想情况下,拐点处(VPL)即是漏极电流达到最大的时刻。

第三阶段:

漏源电压VGS从平台电压(也称为米勒平台)VPL上升至VPR,ID会在此过程中某点达到最大值,VDS在t3时刻达到最小值(器件完全导通),t2至t3时刻的QGD是注入到栅极的电荷量。随着VGS继续上升,会看到VGS斜率迅速下降,并且在某些情况下其斜率会降低到0斜率。这时,可以认为VGS进入电压平台阶段,这一阶段会持续t2至t3时间。图5所示的平台阶段的电压斜率是由从栅极看到到的总电荷量减少情况决定的,而这一电荷量的变化取决于Cgd与VGD的乘积,与在第二阶段的分析情况一样,如果VDS与Cgd的所代表的电荷量迅速降低,这时就会有更多的栅极电流流入Cgd以适应这样的电荷量变化,因此流动到Cgs的电荷量就会减少,这样就会造成VGS的斜率降低,如果VGD*Cgd变化足够大,所有的栅极电流都需要去补偿这种变化时,栅极电压斜率就会为0斜率。因此在实际测试过程中,将会发现对于超低开关损耗的MOSFET,平台电压斜率将不为0斜率,而对于Qg参数较大的MOSFET器件以及IGBT,平台电压降出现0斜率。

当VDS降低时Cgd将增加,VDS降低至ID*RDS(on)时,将停止降低,此时将达到曲线的第二个拐点VPR,此时t=t3。

第四阶段:

在第四阶段,VGS从VPR上升至VDR,漏极电流保持最大,漏源电压VDS保持最小,此时从t0至t4可以观察得到Qg。当VDS降低到ID*RDS(on)时,VGS将以新的斜率上升,此时VDS将不再变化,有恒流源驱动的栅极电流将再次绝大部分流入Cgs。而此时栅极电压上升斜率将比在第一阶段是略低,这是由于此时Cgd已经随着VGD的降低而变大了许多,并且与Cgs寄生电容容值接近。栅极电流将同时对Cgs和Cgd充电,原理与第一阶段相同,并且这是漏极电压低于栅极电压,因此Cgs和Cgd均与电压无关为一常量。

从图6 可以清楚地看出对于工作在开关状态下的MOSFET,在t1之前,漏极电压最高但漏极电流近似为零;在t3之后漏极电流达到最大,此时的漏极电压又近似为零,器件在这两个阶段的自身损耗P近似为零。其功率损耗集中在t1到t2的开启和t2到t3的平台阶段,MOSFET在关断时的波形是图6的镜像,损耗同样集中在这两个阶段。在同样的驱动条件下,器件的栅电荷越大,t1到t3的时间就越长,器件在开关时的损耗就越大,因此栅电荷对于工作在开关状态下的MOSFET是一个非常重要的参数。

特别强调的是图6中所示的漏极电压VD 和漏极电流ID 与栅电荷变化时的对应关系,是用高速恒流源做负载时的结果,如采用电阻做负载,漏极电流ID的变化将会是随漏极电压VD变化而滞后,从而影响VGS在T2处的波形和T2到T3的平台部分,直接影响栅电荷的测试结果。

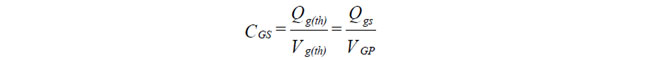

美军标MIL-STD-750E 3471.2中定义的栅电荷测试分解的更为详细。栅电荷测试各部分的定义如下:

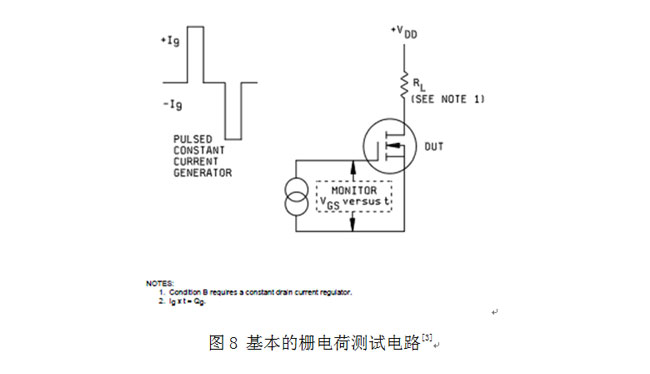

图8 是美军标MIL-STD-750E 3471.2中给出的N沟道MOSFET栅电荷基本测试电路。转换栅极恒流源脉冲和VDD极性,就可以对P沟道MOSFET测试。

美军标中对栅电荷测试电路中漏极负载做了两种规定:

Condition A中规定漏极使用电阻RL作为负载进行测试,

电阻值按下述公式确定:

RL = VDD / ID

被测器件截止状态时的漏极电压VDD应设定在器件漏源击穿电压的50%到80%之间,同时规定ID >= 100 mA 。

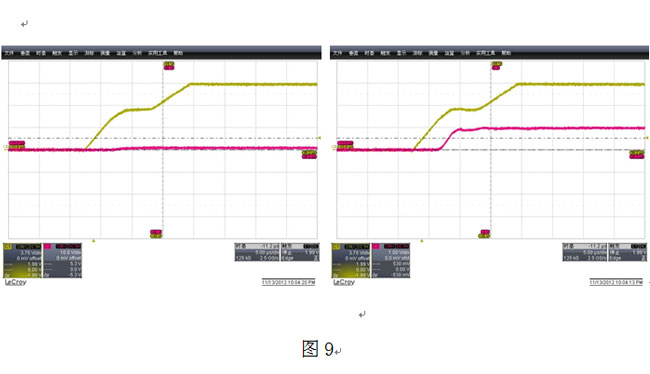

这种测试电路非常简单,但由于在被测器件开启和关断的过程中ID电流随VDS变化,ID对栅-漏电容的充电的变化会使VGS曲线(图5)在t1到t2第一拐点处过于弯曲变得圆滑,无法准确确定拐点的时间坐标,从而直接影响Qgs和Qgd的测量。我们在LX9600栅电荷测试系统[4]上做了对比测试,图9中的左图就是使用电阻负载时的Vgs波形(黄色);

LX9600测得漏极电阻负载(左)和一般恒流源负载(右)的Vgs比较

被测器件IRF640

Condition B中漏极D使用恒流源替换RL负载,测试电路比较复杂,对漏极恒流源的要求非常高。恒流源必须是浮动的,在被测器件导通时能承受VDD的高压,电压范围从二十几伏到一千伏左右,在被测器件截止时有非常低的饱和压降,最重要的是这个恒流源的动态响应必须非常快,响应时间应和被测器件的响应时间大致相同,否则会影响Qgd的特性曲线(图5 中t2-t3部分),图9中的右图是一个低速恒流源做负载时Vgs(黄色)的特性曲线,明显看出t2-t3阶段的曲线不平坦,而且有跌落。

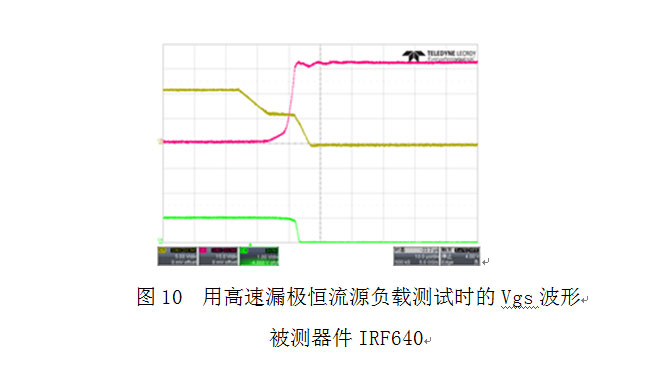

图10是采用高速恒流源作为负载时的Vgs特性曲线,测试结果与IRF640器件手册给出的特性曲线(图2)完全吻合。

图3和图4所示均是MOSFET导通时的特性曲线,器件关断时,会释放电荷,这是一个与导通相反的过程,虽然实际应用中导通和关断可能使用不同的驱动电路,但栅极电荷对其影响、原理分析与参数数值均相同。

因为MOSFET开启和关断时的栅极电荷是相等的,所以在实际测试中一般采用电压脉冲开启、恒流关断的方法去测量栅电荷,这样控制电路比较简单、并且安全可靠。图9是采用关断时测量的栅极电压(黄色)和漏极电压(红色)、电流(绿色)波形,可以看出VGS与图8中的波形是镜像的。

美军标测试条件A和B对栅极电流Ig的规定是相同的,要求栅极恒流源从被测器件关断到导通或导通到关断的过度时间大约50uS 。Ig 的设定值根据芯片尺寸而定,范围从0.1mA 到 5mA 。

实践中对于一些大功率器件,特别时IGBT组件,是由多个器件并联组成的,其输入电容非常大,如果Ig 设定值小,会导致被测器件在t1到t3阶段(图6)时间过长,器件会迅速发热甚至损坏。因此应根据器件手册给出的输入电容等参数增大栅极恒流源的Ig值。美军标中建议栅极恒流源有数十毫安的输出能力,一般工程上设计一个0.1mA―200mA输出的可编程栅极恒流源就可以基本满足全部测试需求。

但增大Ig时应避免输入分布参数(主要是感抗)的影响,否则在示波器上观察到的Vgs电压波形就不能真实反映栅电荷的变化,在工程实践中必须重视栅极恒流源与被测器件之间的连接和布局。

无论采用A、B那种测量条件,美军标中都规定测试时管壳温度应在 +25°C。实际上温度的变化对栅电荷这个参数影响较小,可根据不同需求来规定测试时对温度的要求,以降低测试成本。

测试用高速数字存储示波器的带宽应大于300M、采样速率 >= 1G,最好有三个以上输入通道,可同时观察栅极电压,漏极电压和漏极电流波形。对于漏极电流的采样应使用高速电流传感器,采样点最好放在源极,以避免漏极一端的分布参数带来的影响。

栅极电压输入通道探头的前端应有缓冲驱动,美军标中采用的是运算放大器CA3240E作为跟随器,其输入阻抗1.5T,输入电流10pA,输入电容4pF,这样可以降低示波器探头引入的误差。

参考文献:

作者介绍:

李力军:从事集成电路、半导体分立器件测试的相关技术研究和系统的开发研制工作三十余年,曾任国家多个重点攻关项目中集成电路测试系统研发子课题的负责人,承担过北京市科委和北京市经信委的多个重大科研项目,开发的半导体分立器件直流参数测试系统BC3193在器件厂家,军工院所,高校等领域得到广泛应用。目前研制的半导体交流参数测试系统LX9600,测试内容涵盖,时间参数、栅电荷、结电容、雪崩耐量、反向恢复时间等交流参数。现任北京自动测试技术研究所副总工程师、北京市科学技术研究院半导体分立器件测试实验室主任,北京励芯泰思特测试技术有限公司总工程师。